ZBasic System Library

199

ZBasic Microcontrollers

written to the TWBR register of the I2C controller. The low two bits of the high byte select a clock divisor

according to the table below. The clock speed of the hardware channel is given by the formula F_CPU /

(16 + 2 * BR * Divisor) where F_CPU is the device’s operating frequency. If the bitRate parameter is

omitted or is zero the value of 66 is used by default.

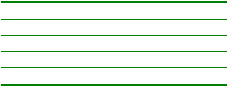

Channel 0 Prescaler Selector Value

Value

Divisor

0

1

1

4

2

16

3

64

For ATxmega-based devices, the I2C bit rate is given by the formula F_CPU / 2 / (5 + rateVal)

where rateVal is the low 8 bits of the bitRate parameter. Rearranging this formula gives an equation

for the bitRate parameter: bitRate = (F_CPU / 2 / F_I2C) – 5 where F_I2C is the desired

I2C clock frequency.

For software channels the bitRate parameter is interpreted as the number of I/O Timer ticks per bit.

For I2C operations, the I/O Timer uses the prescaler specified by Register.TimerSpeed1. With the

default prescaler of 1, each I/O Timer tick represents approximately 68nS with a main clock frequency of

14.7MHz. If the bitRate parameter is omitted or is zero the value of 74 is used by default. Due to

processing overhead, the minimum attainable bit time is approximately 60 CPU cycles (4µS at 14.7MHz).

See the Resource Usage subsection "I2C Controllers" for information on the available I2C hardware

channels and the corresponding clock and data pins.

Examples

Call OpenI2C(0, 0, 0)

' open the hardware channel at 100KHz

Call OpenI2C(2, 19, 20)

' open channel 2 using pins 19, 20

Call OpenI2C(1, C.3, A.1, 74)

' open channel 1 at 200KHz

Resource Usage

The I2C routines utilize the I/O Timer to regulate the bit timing for the software channels. While sending

or receiving I2C data, the corresponding timer busy flag will be True indicating that the I/O Timer is in use.

Compatibility

This subroutine is not available in BasicX compatibility mode.

See Also