ZBasic System Library

25

ZBasic Microcontrollers

receive all of the data that an SPI device requires using a single call to SPICmd(), then that SPI device is

usable with the ZX models that utilize an external EEPROM.

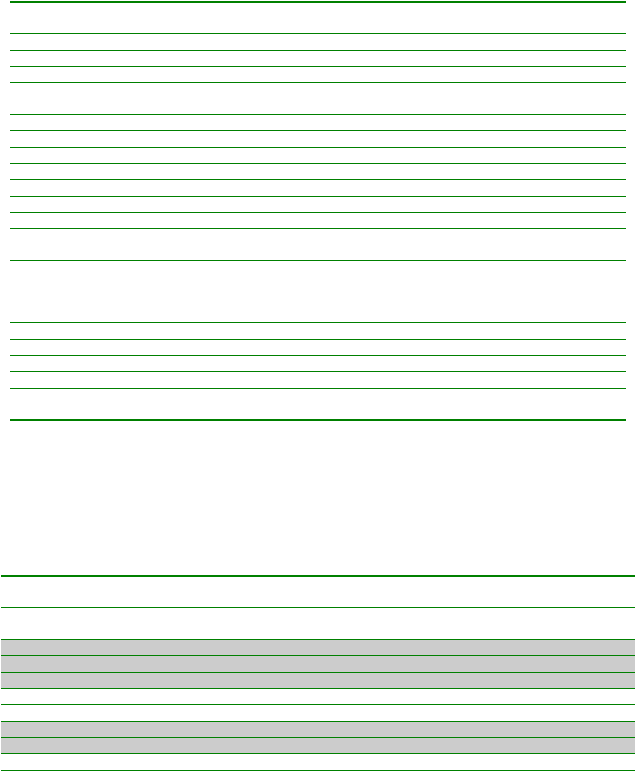

The table below indicates which ZX devices use an external EEPROM for user program storage and, if

so, the I/O pin used for the chip select. For devices that do not use an external EEPROM for user

program storage, the indicated chip select pin can be used for general purpose I/O with the proviso that if

the SPI controller is used in the application program the chip select pin must either be an output or it must

be held high during SPI transactions.

SPI EEPROM Usage and Control/Data Pins By Controller Index for ZX Devices

ZX Device

Uses SPI

EEPROM

Ctrl.

Idx.

CS

Pin

SCK

Pin

MOSI

Pin

MISO

Pin

ZX-24, ZX-24a, ZX-24p

Yes

0¹

B.4

B.7

B.5

B.6

ZX-40, ZX-40a, ZX-40p

Yes

0

5, B.4

8, B.7

6, B.5

7, B.6

ZX-44, ZX-44a, ZX-44p

Yes

0

44, B.4

3, B.7

1, B.5

2, B.6

ZX-24x, ZX-24u

No

0¹

1

D.4

8, C.4

D.7

5. C.7

D.5

7, C.5

D.6

6, C.6

ZX-24n, ZX-24r, ZX-24s, ZX-24t

No

0¹

B.4

B.7

B.5

B.6

ZX-40n, ZX-40r, ZX-40s, ZX-40t

No

0

5, B.4

8, B.7

6, B.5

7, B.6

ZX-44n, ZX-44r, ZX-44s, ZX-44t

No

0

44, B.4

3, B.7

1, B.5

2, B.6

ZX-328n, ZX-328l

No

0

16, B.2

19, B.5

17, B.3

18, B.4

ZX-32n, ZX-32l

No

0

14, B.2

17, B.5

15, B.3

16, B.4

ZX-1281, ZX-1281n

No

0

10, B.0

11, B.1

12, B.2

13, B.3

ZX-1280, ZX-1280n

No

0

19, B.0

20, B.1

21, B.2

22, B.3

ZX-32a4

No

0

1

24, D.4

23, C.4

27, D.7

17, C.7

25, D.5

15, C.5

26, D.6

16, C.6

ZX-128a1

No

0

1

2

3

29, D.4

19, C.4

39, E.4

49, F.4

32, D.7

22, C.7

42, E.7

52, F.7

30, D.5

20, C.5

40, E.5

50, F.5

31, D.6

21, C.6

41, E.6

51, F.6

ZX-24e, ZX-24ae, ZX-24pe, ZX-24pu

Yes

0

24, B.4

21, B.7

23, B.5

22, B.6

ZX-24ne, ZX-24nu, ZX-24ru, ZX-24su

No

0

24, B.4

21, B.7

23, B.5

22, B.6

ZX-128e, ZX-128ne, ZX-1281e, ZX-1281ne

No

0

28, B.0

27, B.1

26, B.2

25, B.3

ZX-328nu

No

0

13, B.2

16, B.5

14, B.3

15, B.4

ZX-24xu

No

0

1

16, D.4

8, C.4

13, D.7

5. C.7

15, D.5

7, C.5

14, D.6

6, C.6

¹ The SPI pins are found along the edge of the board between pins 1 and 24

For generic target devices, user programs are always stored in internal Flash memory. The table below

shows the chip select pin associated with each on-chip SPI controller as well as the SPI control/data pins.

As described above, the SPI chip select pin(s) may be used for general purpose I/O except that if the

related SPI controller is used in the application program the chip select pin must either be an output or it

must be held high during SPI transactions

SPI Control/Data Pins By Controller Index for Generic Target Devices

Target Device

Pkg.

Ctrl.

Idx.

CS

Pin

SCK

Pin

MOSI

Pin

MISO

Pin

tiny24, tiny24A, tiny44, tiny44A, tiny84, tiny84A,

tiny2313, tiny2313A, tiny4313, tiny1634

all

-

-

tiny48, tiny88

P28

0

16, B.2

19, B.5

17. B.3

18, B.4

T28

12, B.2

15, B.5

13. B.3

14, B.4

T32

14, B.2

17, B.5

15. B.3

16, B.4

tiny441, tiny841

S14

0

6, A.7

9, A.4

7, A.6

8, A.5

Q20

15, A.7

1, A.4

16, A.6

20, A.5

tiny87, tiny167

S20

0

9, A.6

8, A.5

7, A.4

3, A.2

T32

11, A.6

10, A.5

9, A.4

31, A.2

tiny828

T32

0

31, C.0

30, D.3

27, D.0

28, D.1