ZBasic System Library

206

ZBasic Microcontrollers

Type

Subroutine

Invocation

OpenSPI(channel, flags, csPin)

OpenSPI(channel, flags, csPin, rxDelay)

Parameter

Method

Type

Description

channel

ByVal

Byte

The SPI channel to open (1-4).

flags

ByVal

integral

Flags controlling the SPI communication.

csPin

ByVal

Byte

The pin for the chip select signal to the device.

rxDelay

ByVal

Byte

The delay time prior to each received byte.

Discussion

This subroutine prepares an SPI channel for use as a master. By default, the hardware SPI controller is

used to implement the SPI protocol but on some devices, a bit-bang implementation can be enabled (see

DefineSPI).

Four channels are supported, numbered 1 through 4. It does not matter if the particular channel has

been previously opened. The flags parameter specifies the characteristics of the SPI communication

as shown in the table below. They must be set to be compatible with the device with which you want to

communicate. See the table below for details. The csPin parameter specifies the pin number that you

wish to control the device’s chip select input. The pin will be made an output and set to the inactive state

(as specified by bit 6 of the flags parameter). Any general purpose I/O pin of the device may be used

as the slave select pin. Note, however, that if the pin dedicated SS pin is not used to select remote

slaves, it must be configured as an output or remain at the logic high state for the duration of an SPI

operation. Also, for ZX devices that use an external SPI EEPROM for program storage (e.g. ZX-24, ZX-

24a), the SS pin is used to select the SPI EEPROM and therefore cannot be used for any other purpose.

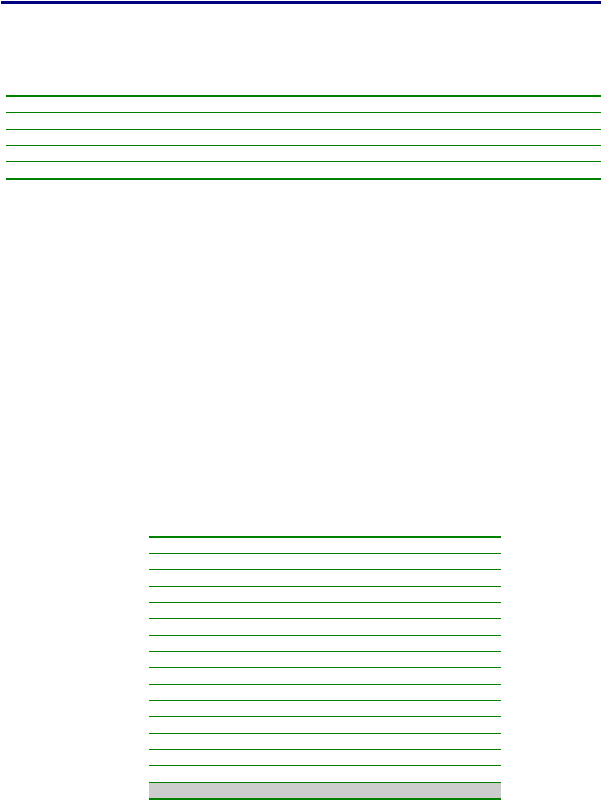

The table below describes the function of the bits of the flags parameter. The shaded entries do not

apply to the software SPI implementation.

SPI Channel Control Bits

Function

Hex Value

Binary Value

Bit Rate f/4

&H00

xx xx xx 00

Bit Rate f/16

&H01

xx xx xx 01

Bit Rate f/64

&H02

xx xx xx 10

Bit Rate f/128

&H03

xx xx xx 11

Clock Phase False

&H00

xx xx x0 xx

Clock Phase True

&H04

xx xx x1 xx

Clock Low at Idle

&H00

xx xx 0x xx

Clock High at Idle

&H08

xx xx 1x xx

Use Hardware SPI

&H00

xx x0 xx xx

Use Software SPI

&H10

xx x1 xx xx

Bit Order – MSB first

&H00

xx 0x xx xx

Bit Order – LSB first

&H20

xx 1x xx xx

Active Low Chip Select

&H00

x0 xx xx xx

Active High Chip Select

&H40

x1 xx xx xx

Double Speed

&H80

1x xx xx xx

The remaining bits are currently undefined but they may be employed in the future. Because of this

possibility, the undefined flag bits should be zero. Bits 3 and 2 taken together specify the SPI mode 0-3,

e.g. xx xx 00 xx specifies mode 0. When using the hardware SPI controller, if the Double Speed bit is set,

the SPI channel will run at twice the frequency specified by the two low order flag bits. The value of f for